长电科技(滁州)有限公司 安徽滁州 239000

摘 要:深圳必易拥有全球领先的电源管理系统的架构和设计能力,并致力于通讯、计算机、消费电子和LED照明等领域的高效智能化电源管理产品的开发、设计、测试及销售。KP1030TPA产品为必易的主打产品,在封装测试中发现产品测试无良率,本文主要通过分析研究找出失效原因,提出改善异常的解决方案,保证产品的正常生产。

关键词:半导体;测试;无良率

1.引言

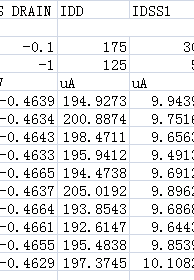

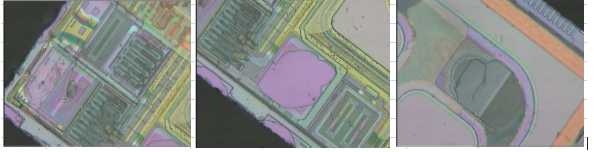

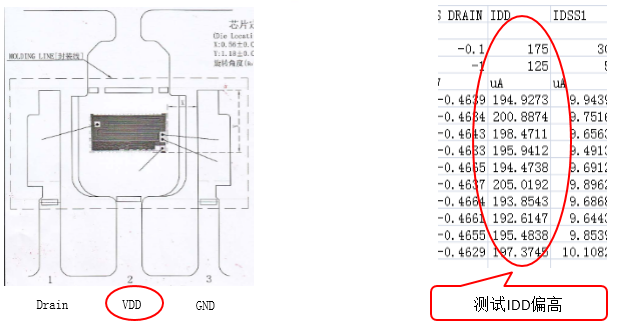

深圳必易KP1030TPA SOT-89-3L(8R)产品之前采用不导电胶进行生产,产品作业良好,测试良率在95%以上,产品量产正常,为增强KP1030TPA SOT-89-3L(8R)产品散热能力,产品改为导电胶进行生产,其余BOM均不变,产品封装后测试无良率,主要测试不良为IDD(静态电流偏高),产品BOM信息(见表1.1),产品布线图(见图1.1),产品测试数据(见图1.2),另相同芯片不同封装 导电胶 TO-92产品封测也是正常,初步怀疑可能为封装制程原因或测试规范较严导致KP1030TPA SOT-89-3L(8R)产品测试无良率。

表1.1 BOM基本信息

| Package | SOT-89-3L(8R) |

| Device | KP1030TPA |

| Die ID | KWTXNH |

| Bonding Drawing | SOT-89-3L(8R)-2361(D) |

| Die Size | 1.47mm*0.73mm |

| Epoxy | 84-1LMISR4 |

| Wire | Φ20um (0.8 mil) Au |

| Lead frame | SOT-89-3L-B(8R)条带 |

| Compound | KL-7000HA |

| Bond pad opening | 0.07mm*0.07mm |

| AL Metal Thickness | 1.2 um |

| CUP Wafer | NO |

图1.1

Brain VDD GND

图1.1

图1.2

2.原因分析

2.1产品腐球分析

备注:产品腐球发现压区损伤。

2.2主要原因分析

备注:可能为球焊参数不匹配导致芯片压区受损。

3. Qual Lot验证情况

3.1 SOT-89和TO-92对比验证

采用同一张圆片进行TO-92和SOT-89不同胶的对比验证

| Customer | Package | BOM | Customer Device | Test |

| 深圳必易 | TO-92 | 84-3J+KL-1000-3LX+Au 20 | KP1030LPA | 97.70% |

| 深圳必易 | TO-92 | 84-1 L+KL-1000-3LX+Au 20 | KP1030LPA | 96.90% |

| 深圳必易 | SOT-89-3L(8R) | 84-1 L+KL-7000HA+Au 20 | KP1030TPA | 无良率 |

| 深圳必易 | SOT-89-3L(8R) | 84-3J+KL-7000HA+Au 20 | KP1030TPA | 97.20% |

备注:通过对比发现,同一张圆片TO-92生产正常,但SOT-89导电胶生产无良率,可以排除来料芯片差异性,同时SOT-89不导电胶生产正常,导电胶生产无良率,故可能为产品本身设计有缺陷。

3.2结果分析

3.2.1切割

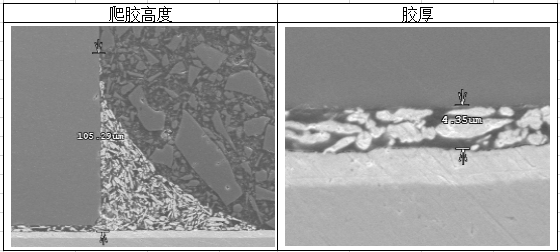

KP1030TPA SOT-89导电胶产品测试无良率,主要为IDD不良,对不良品的爬胶高度和胶厚进行确认,胶厚和爬胶高度均正常。

3.2.2测试数据分析

深圳必易KP1030TPA SOT-89-3L(8R) 导电胶产品更换不同料饼测试良率均为0,主要测试不良是IDD(静态电流)偏高。

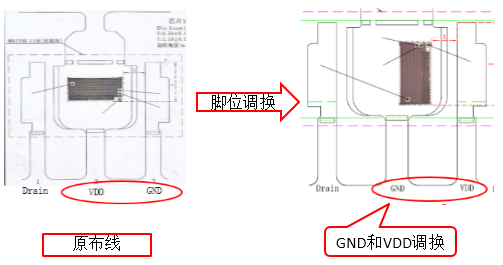

经分析KP1030TPA SOT-89导电胶产品,芯片背面与VDD导通,测试时,芯片背面可能与VDD导通。使用SOT-89封装,模拟TO-92的打线,产品的测试脚位进行调换,使用导电胶、金丝进行试验。

3.3 KP1030TPA SOT-89改变脚位工程批验证

投两批工程批进行验证,一批为导电胶+调换脚位;一批为不导电胶+正常脚位(此为正常生产产品),对比确认两批测试情况。

| 批次 | 调换脚位批 | 正常量产批 |

| 工作令 | C1601B211 | C1601B212 |

| 封装形式 | SOT-89-3L(8R) | |

| 芯片名称 | KWTXNH | |

| BD图画 | SOT-89-3L(8R)-2599(临) | SOT-89-3L(8R)-2577 |

| 装片胶 | 84-1L | 84-3J |

| 焊线 | Φ20 HD3 Au | |

| 塑封料 | KL-7000HA | |

| 脚位 | Drain GND VDD | Drain VDD GND |

3.3.1 工程批测试结果

3.3.2结论

试验情况正常,两批试验测试良率均在95%附近,测试良率相近。

在更换脚位后,导电胶也可以适用此款产品,所以导电胶的使用并不是零良率的根本原因。

综合以上试验分析,我们得出以下结论:原来的产品,VDD作用在基岛,使用导电胶连接芯片背面,致使IDD(静态电流)偏大。

3.3.3改善方案

使用不导电胶。

如要使用导电胶,基岛不能作为VDD工位(因为IDD的测试条件是:VDD加压6.1V,测试VDD脚电流,SPEC=125-175uA)。

4.总结

通过多次验证确认深圳必易KP1030TPA SOT-89导电胶产品测试无良率为产品本身设计原因,改变产品打线方式,调换产品对应脚位,产品测试正常,目前此产品已正常生产,需求 4KK/M,通过对不良品的分析,开阔了分析的眼界,增加了的知识储备,为客户挽回了损失,为长电带来了客观的收益。

参考文献

[1] 陈一梅,黄元庆. MEMS 封装技术[J].传感器技术,2005(3).

1