陕西华经微电子股份有限公司 西安 710065

摘要:文中针对厚膜混合集成高速高压驱动电路进行了原理分析,并对产品的技术难点、解决措施和关键工艺技术问题进行阐述。

关键词:高速高压驱动电路 ;厚膜混合集成;产品可靠性

1.概述

混合集成电路高速高压驱动电路, 是输入电压为+5V和-50V,由于负压高,而且静态电流要求小的原因,因此采用分立元件进行设计。此方案能够很好的将静态电流降低到12ma以下,并且满足用户的使用要求,组装工艺方面采用厚膜芯片混合集成技术;结构方面按要求采用双列直插金属平行缝焊外壳。

2.产品的技术指标和尺寸:

主要的技术指标如下:

1.电源电压:VCC=5.0V±0.5V,VEE=50.0V±0.5V;

2.输入信号: TTL电平,占空比50%,频率100Khz;

3.输出高电平电流:≥150 mA;

4.输出低电平电压:≥-40V,≤-50V;

5. 静态电流:≤12 mA;

6. 上升时间、下降时间:≤140 ns;

7. 传输延迟时间:≤450 ns;

8.环境条件:工作温度-55℃~+125℃。

9.外形尺寸:21.00×18.00×5.8mm3;

3.设计方案和原理图

按照该项目的各项要求,进行分析,其特点是:(1)体积小,输出功率大,静态消耗小。(2)输出脉冲的延迟小,并且对脉冲的前后沿要求高:在所要求的宽温度范围(+125℃~-55℃)内为140ns,这样在常温只能控制在几十ns的水平。(3)所提供的电源较为特殊是:+5V和-50V,这样要采用高速集成电路,一般要设计辅助电源,但仅此一项所消耗的电流就超过整机的消耗电流指标等诸多问提以及本项目的特殊性,在前期方案论证阶段参考了大量有关资料并进行相关的实验论证,在此基础上提出了以下原则:(1)采用高速开关电路以保证脉冲信号的有效传输,特别是脉冲延迟和前后沿的要求。(2)电路设计要简洁,尽可能地减少电流消耗和在电路中的传输延迟。(3)在方案中不增加辅助电源。

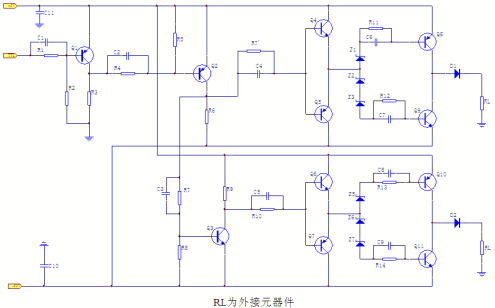

本产品的实际电路如下图所示:

图1电路原理图

3.1工作原理

由于输入信号为TTL方波,以地电平为基准。但要求电路最终输出的脉冲信号,其高低电平应分别接近电源电压:Vcc(高电平:+5V),和Vee(低电平:—55V),为此必须首先将以地电平为基准的TTL输入方波转换为以电源Vcc为基准的方波,再分为两路分别进入后级:脉冲同相和脉冲反相放大电路进行放大。最后再分别进入同相和反相脉冲驱动及功放输出电路。这样处理后最终得到所要求的高低电平分别为接近电源Vcc和Vee的脉冲高压信号输出。

3.2输入及分配电路

这部分电路接受输入信号为TTL方波后,首先反相并转换成以Vcc为基准的方波,再由Q2开关电路反相得到同相信号,并在A点输出高低电平分别接近电源Vcc和Vee的方波信号。本级是带有加速电容的高速开关电路,是整个电路的关键部分;当无信号输入时整个电路处于封闭状态,全部电路的静态消耗电流为最小值。当输入信号为高电平时,整个电路翻转。

3.3脉冲驱动和功率输出级电路

同相及反相回路的输出驱动和功率输出级电路采用同样的电路形式,包含放大电路和驱动电路两部分,因电路要求同相电路和反相电路具有较大的输出功率,所以在功率输出级前采用一级驱动电路用以有效地推动功率输出级电路,该驱动电路由Q4,Q5互补对称晶体管组成无变压器放大电路,工作在丙类工作状态,静态时消耗电流趋于零,有效地降低了静态消耗电流。功率输出级电路采用Q8,Q9对管输出,为保证输出波形及脉冲前后沿的要求,必须加偏置电压,偏置电压大小为正电源电压与负电源电压的代数和,即Z1+Z2+Z3=Vcc+Vee。

4结构及可靠性设计

4.1结构设计

根据电性能指标和原理图以及用户需要外形尺寸小于23×18×5.6 mm3的要求,因此选用43所生产的双列直插14线金属平行缝焊封装外壳。

4.2可靠性预计

可靠性设计贯穿于整个产品设计的始终。在线路设计方面、元器件选用方面多做综合考虑,简化线路,减少元器件数量,增强元器件性能的余量设计。根据GJB/Z299A-91《国家军用标准可靠性Ⅲ》中的电子设备可靠性预计手册和该电路的组成(膜电阻9只、片电容11只、片电阻8只、三极管11只、二极管2只、稳压管6只、)作以计算分析(其中N表示元器件个数,其他符号见(GJB/Z299A-91),预计该产品可靠性为1.66×105小时。

5技术难点、解决措施和关键工艺技术

5.1技术难点

1)静态微功耗

由于技术要求静态消耗电流小仅为12mA而且外壳小并且必须适应在高低温度下都能正常工作,所以电路的消耗电流需要严格控制。这在摸底试验初期就已经体会到:消耗电流大,外壳温升高。为此:(1)在方案选择和电路设计上进行了一系列工作,如上所述:把输入级做为总开关,当无信号输入时整个电路封闭,驱动级和工放级都设计在丙类工作状态等。(2)在生产工艺方面进行优化,加强散热处理等,最终把静态消耗电流将低到4.8~6.0mA(技术要求为12mA),确保三温静态消耗电流小。

2)高压负电平正负不对称输出

电路输入为TTL信号,输出波形要求工作电压正负不对称,输出负电压达到50V,又不能增加辅助电源,为此全部采用晶体管级联电路,这样在不使用辅助电源的情况下,输出脉冲的高低电平分别接进正负电源。

3)技术要求脉冲延迟小,前后沿的要求更小

为此采用高速电路,电路简洁,减小各级延迟,并且在最后一级进行了整形,控制常温的前后沿要求在60ns以下,从而保证了在高低温度下脉冲的沿迟和前后沿要求。

5.2解决措施

针对难点1,第一步采取的措施是:选用分立元件进行设计,在满足产品前后沿时间,使电路静态电流小;

针对难点2,由于输出负压要求高,转化速率快,负相电路的PNP管就要求比较严格,经过反复实验,确定PNP管型号。

5.3平面布图和组装工艺

全金属屏蔽、全密封抗机械冲击、防静电保护,根据机械环境试验的要求,充分考虑各种环境的危害,加强贴片焊接和封装等工艺控制,使产品可靠工作。

在布版上,综合考虑线路特点、工艺特点,适合批量生产要求,避免二次导带和介质布图,提高一次合格率。适当制定电阻导带面积,尽量缩小布图面积;合理分配管芯分布面,保证在腔体内键合的可操作性。

工艺方面,选用导热性好的粘接料;管芯压焊采用25μm的金丝方案。

基片印刷,由于需要在基片上印刷的导带较多,所以印刷时我们经过大量的试验,确定了此项工艺的技术参数。

封装方面,采用平行缝焊,保证密封可靠。

基片粘结:考虑到产品要做振动,基片与底座的粘接必须牢固以抗振动,我们经过大量的试验,最后确定粘接前先将底座上与基片接触的表面打磨成毛面,然后在基片上均匀的涂抹上高温环氧,这样基片与底座的粘接就会很牢固,满足振动要求。

6.产品特点、存在的问题和努力的方向

该产品具有体积小,控制可靠,输出波形失真小,可靠性高,稳定性能好,温度漂移低等突出特点。由于采用全表面贴装结构,元器件全部小型化、微型化、管芯化,全金属平行缝焊封装结构,密封、屏蔽性好。由于采用了厚膜电阻,加之生产过程中误差参数控制较严,内部电位点精确,使得电性能一致性好。该产品的不足就是采用分立元件离散型比较高,就必须选用精度高的元器件,导致产品的成本高,目前该产品方案已进行更改和调整,采用集成电路进行控制,产品的合格率和可靠性大大提高。今后努力将产品做成系列化产品,进一步缩小体积,扩大产品的应用范围。

参考文献:

方培敏,张国华,最新集成电路应用指南 北京:电子工业出版社,1996

1